PDP-8/L Renovering

Re: PDP8 Renovering

Tack, perfekt.

Nu gick det att hänga med.

Det finns alltså specialregister som är till för konsol-in och konsol-ut.

Och register/bitar som visar status för dessa.

Och acumulatorn verkar vara default-register som används vid dessa operationer.

Nu gick det att hänga med.

Det finns alltså specialregister som är till för konsol-in och konsol-ut.

Och register/bitar som visar status för dessa.

Och acumulatorn verkar vara default-register som används vid dessa operationer.

Re: PDP8 Renovering

Nja, det är enklare än så.

Om du tänker dig en vanlig UART, så har den 8 ingångar för data, och 8 utgångar. Vidare har en en pinne som indikerar om transmit är upptagen eller ej, och en pinne som indikerar om det tagits emot en byte eller inte. Till slut har den även en strobe för läsning respektive skrivning.

Tänk dig nu att du hänger denna UART på bussen på en PDP-8. Instruktionen TLS berordar CPU (via ett par signaler på bussen) att lägga ut ackumulatorn på bussens datapinnar, och drar strobe för skrivning. Därmed laddas transmit-delen av din UART med data från bussen, och börjar klocka ut dessa på seriepinnen. Medans detta sker så ligger pinnen för transmit aktiv, och visar därmed att transmit är upptagen.

TSF-instruktionen kommer antingen göra så att processorn gör en SKIP över nästa instruktion eller inte. SKIP är en signal på bussen som device kan aktivera för att få processorn att göra SKIP. En TSF kopplar helt enkelt in transmit busy-signalen från din UART till SKIP-signalen i processorn.

Mottagning fungerar på samma sätt. När din UART detekterar en start-bit, så börjar den klocka in data från serielinan. När rätt antal bitar har klockats in så dras det i pinnen som säger att nu finns det data. KSF gör samma trick att koppla ihop denna signal från UART med SKIP-signalen in till processorn.

KRB i sin tur gör att data från UARTs utgångar (där mottagen data finns), läggs ut på bussen (med hjälp av strobe, som också återställer pinnen som indikerar att data finns), och sedan dras ett par signaler till som beordrar CPU att kopiera data från bussen till till ackumulatorn.

Så det finns egentligen inte en massa specialregister, om du inte tänker på att UART alltid har ett register (eller två) som seriell data klockas in/ut på. Och det finns bara en ackumulator, och i princip alla operationer i en PDP-8 görs mot ackumulatorn. Det finns inte så värst mycket fler register alls. Du har PC och AC, som är 12 bitar. IF och DF som är 3 bitar, och som används som en utökning av addresserna. Sedan har du LINK, som är en bit, och som oftast fungerar som en 13:e bit vid addition (lite carry över den). Sedan är det nog inget mer jag kommer på på rak arm.

Ja, det finns ju en interrupt enable, som är en bit, och en interrupt inhibit på en bit. Bergis en eller par sådana statusbitar till kan du hitta om du letar. Men "register" som sådana brukar jag bara betrakta AC.

Om du tänker dig en vanlig UART, så har den 8 ingångar för data, och 8 utgångar. Vidare har en en pinne som indikerar om transmit är upptagen eller ej, och en pinne som indikerar om det tagits emot en byte eller inte. Till slut har den även en strobe för läsning respektive skrivning.

Tänk dig nu att du hänger denna UART på bussen på en PDP-8. Instruktionen TLS berordar CPU (via ett par signaler på bussen) att lägga ut ackumulatorn på bussens datapinnar, och drar strobe för skrivning. Därmed laddas transmit-delen av din UART med data från bussen, och börjar klocka ut dessa på seriepinnen. Medans detta sker så ligger pinnen för transmit aktiv, och visar därmed att transmit är upptagen.

TSF-instruktionen kommer antingen göra så att processorn gör en SKIP över nästa instruktion eller inte. SKIP är en signal på bussen som device kan aktivera för att få processorn att göra SKIP. En TSF kopplar helt enkelt in transmit busy-signalen från din UART till SKIP-signalen i processorn.

Mottagning fungerar på samma sätt. När din UART detekterar en start-bit, så börjar den klocka in data från serielinan. När rätt antal bitar har klockats in så dras det i pinnen som säger att nu finns det data. KSF gör samma trick att koppla ihop denna signal från UART med SKIP-signalen in till processorn.

KRB i sin tur gör att data från UARTs utgångar (där mottagen data finns), läggs ut på bussen (med hjälp av strobe, som också återställer pinnen som indikerar att data finns), och sedan dras ett par signaler till som beordrar CPU att kopiera data från bussen till till ackumulatorn.

Så det finns egentligen inte en massa specialregister, om du inte tänker på att UART alltid har ett register (eller två) som seriell data klockas in/ut på. Och det finns bara en ackumulator, och i princip alla operationer i en PDP-8 görs mot ackumulatorn. Det finns inte så värst mycket fler register alls. Du har PC och AC, som är 12 bitar. IF och DF som är 3 bitar, och som används som en utökning av addresserna. Sedan har du LINK, som är en bit, och som oftast fungerar som en 13:e bit vid addition (lite carry över den). Sedan är det nog inget mer jag kommer på på rak arm.

Ja, det finns ju en interrupt enable, som är en bit, och en interrupt inhibit på en bit. Bergis en eller par sådana statusbitar till kan du hitta om du letar. Men "register" som sådana brukar jag bara betrakta AC.

- hcb

- Moderator

- Inlägg: 6085

- Blev medlem: 23 februari 2007, 21:44:50

- Skype: hcbecker

- Ort: Lystrup / Uppsala

- Kontakt:

Re: PDP8 Renovering

anders_bzn:

bqt: Tack för den intressanta utläggningen.

Båda (och andra): Det ni gör är sann kulturhistoria.

bqt: Tack för den intressanta utläggningen.

Båda (och andra): Det ni gör är sann kulturhistoria.

Re: PDP8 Renovering

För att uttrycka det bqt skriver fast med de senaste fräcka uttrycken så kan man säga att UART'en har ett eget adress-space som nås med speciella UART-instruktioner (TLS, TSF, KRB, KSF).

- anders_bzn

- Inlägg: 5928

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Wikipedia har en bra artikel om PDP8: http://en.wikipedia.org/wiki/Pdp8

PDP-8 har åtta grundinstruktioner och de som hanterar konsolen (TLS, TSF, KRB, KSF) är IOT (Input-Output Transfer) instruktioner. De börjar alla med 6xxx (OP-koden).

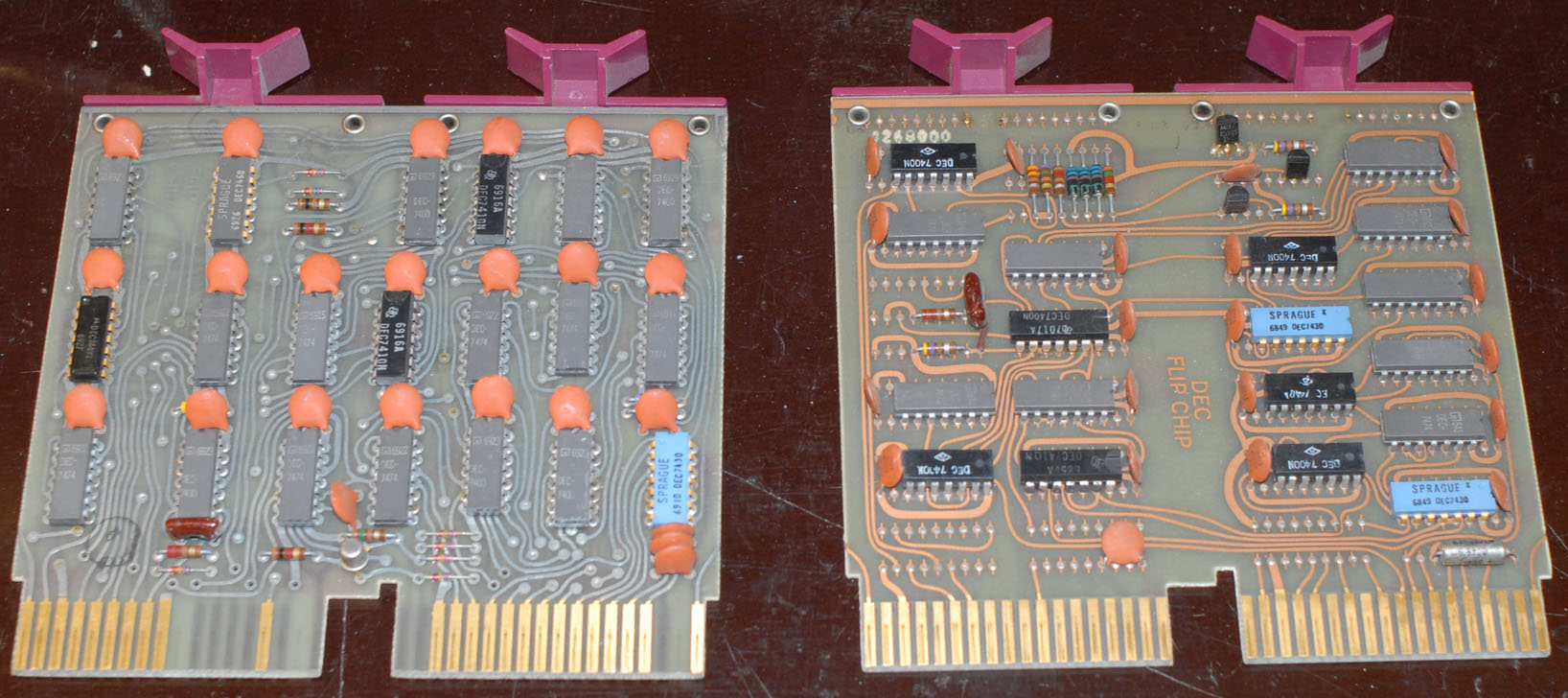

Detta är "UARTEN" eller teletype interfacet RX till vänster och TX till höger. För att få ett komplett interface behöves även ett kort som är BAUD-rate generator och ett kort som gör om TTL nivåerna till det fysiska interfacet (strömslinga alt RS232). Dessa kort är det jag postade här.

Nu visade sig det att FTDI chippen inte klarar 110 baud som native baudrate utan man måste sätta upp chippen manuellt, det betyder att man inte kan öppna porten i ett terminalprogram för då blir baudraten helt fel. Detta betyder att man måste koda lite...

Sen stoppade jag i korten och mätte på utgången med oscilloskopet och körde det första enkla programmet som bqt postade:

Och det körde faktiskt som det skulle, men någon seriedata fick jag inte ut, bara någon dip i kurvan som kom med en frekvens på 11Hz (detta är bra, ty 110 baud är 11 tecken per sekund!).

Så jag stoppade i mitt andra M707 (så heter TX kortet) och testade med det. Resultatet blev att programmet fastnade i TSF, JMP -1 loopen för kortet tyckte aldrig att det sänt färdigt. Detta betyder att detta kortet också var trasigt fast på ett annat sätt än det första.

Dessa två korten är de mest komplexa i hela PDP:n, inga andra kort har så många kretsar. Skiftregistret är uppbyggt av åtta flip-floppar och totalt på kortet sitter det åtta 7474 med två flip-floppar i varje kapsel. Dessa är ökända för att gå sönder (bland oss som lagar PDP-8). Så det blir att hänga på logikanalysatorn...

Edit: Schemat på TX-kortet finns här: http://www.abc80.net/docs/pdp8/modules/ ... _rev_D.pdf

Edit: Stavning

PDP-8 har åtta grundinstruktioner och de som hanterar konsolen (TLS, TSF, KRB, KSF) är IOT (Input-Output Transfer) instruktioner. De börjar alla med 6xxx (OP-koden).

Detta är "UARTEN" eller teletype interfacet RX till vänster och TX till höger. För att få ett komplett interface behöves även ett kort som är BAUD-rate generator och ett kort som gör om TTL nivåerna till det fysiska interfacet (strömslinga alt RS232). Dessa kort är det jag postade här.

Nu visade sig det att FTDI chippen inte klarar 110 baud som native baudrate utan man måste sätta upp chippen manuellt, det betyder att man inte kan öppna porten i ett terminalprogram för då blir baudraten helt fel. Detta betyder att man måste koda lite...

Sen stoppade jag i korten och mätte på utgången med oscilloskopet och körde det första enkla programmet som bqt postade:

Kod: Markera allt

.=200 / Startaddress

LOOP, IAC / Öka ackumulatorn med 1.

TLS / Ladda transmit med AC (transmit för konsol-UART, även om det faktiskt är diskret logik)

TSF / Skippa om transmit done

JMP .-1 / Loopa. Blir med andra ord en loop som väntar tills transmit är done.

JMP LOOP / Hoppa till början igen, och upprepa.Så jag stoppade i mitt andra M707 (så heter TX kortet) och testade med det. Resultatet blev att programmet fastnade i TSF, JMP -1 loopen för kortet tyckte aldrig att det sänt färdigt. Detta betyder att detta kortet också var trasigt fast på ett annat sätt än det första.

Dessa två korten är de mest komplexa i hela PDP:n, inga andra kort har så många kretsar. Skiftregistret är uppbyggt av åtta flip-floppar och totalt på kortet sitter det åtta 7474 med två flip-floppar i varje kapsel. Dessa är ökända för att gå sönder (bland oss som lagar PDP-8). Så det blir att hänga på logikanalysatorn...

Edit: Schemat på TX-kortet finns här: http://www.abc80.net/docs/pdp8/modules/ ... _rev_D.pdf

Edit: Stavning

- Anahka1975

- Inlägg: 1303

- Blev medlem: 30 augusti 2006, 21:49:46

- Ort: Säffle

Re: PDP8 Renovering

Imponerande jobb du lägger ner.

Med risk för att framstå som en totalidiot måste jag ändå fråga vad en sådan här burk har används till, var hittade man dessa förr?

Med risk för att framstå som en totalidiot måste jag ändå fråga vad en sådan här burk har används till, var hittade man dessa förr?

Re: PDP8 Renovering

Tillverkning (NC-maskiner) processindustri (papper, stål o.s.v.).

I princip överallt där man idag t.ex hittar en PLC eller annan dator.

Det var den tidens generella "dator". Det skrev även administrativa

system till dom. Vanliga bokföringsrutiner. Kanske dock vanligare på de

masknerna som kom efter PDP11 o.s.v, med lite ordentliga diskar.

På Ericsson hade i en PDP8e som styrde en sekvenseringsmaskin, d.v.s

en maskin som bandade om axiella komponenter (motstånd, dioder

och mindre kondingar) för att passa monteringsordningen

på kretskorten.

Alltså den maskin som fixar banden med komponenter som senare ska monteras

i en sådan här : http://www.youtube.com/watch?v=ktCJ6y-WN2U.

Notera att komponenterna kommer blandade på bandet, det var maskinen som

fixade det som hade en PDP8 hos oss...

Den här är lite cool också. En PDP8 som bootar OS8 från en RK05 disk (2.5 MB):

http://www.youtube.com/watch?v=ByLp9A1nn7U.

Disken är öppen så läshuvudet syns...

Och datorspel är så klart inget nytt. PDP8, en VT52 terminal och "Adventure" :

http://www.youtube.com/watch?v=TJdq3gK6M78

Och en öppen RK05'a som kör en disk test (från en PDP8) :

http://www.youtube.com/watch?v=Laz-bG8eXYM

http://www.youtube.com/watch?v=5rt8kAcyU4Q

http://www.youtube.com/watch?v=qIXfkZX2XG4

I princip överallt där man idag t.ex hittar en PLC eller annan dator.

Det var den tidens generella "dator". Det skrev även administrativa

system till dom. Vanliga bokföringsrutiner. Kanske dock vanligare på de

masknerna som kom efter PDP11 o.s.v, med lite ordentliga diskar.

På Ericsson hade i en PDP8e som styrde en sekvenseringsmaskin, d.v.s

en maskin som bandade om axiella komponenter (motstånd, dioder

och mindre kondingar) för att passa monteringsordningen

på kretskorten.

Alltså den maskin som fixar banden med komponenter som senare ska monteras

i en sådan här : http://www.youtube.com/watch?v=ktCJ6y-WN2U.

Notera att komponenterna kommer blandade på bandet, det var maskinen som

fixade det som hade en PDP8 hos oss...

Den här är lite cool också. En PDP8 som bootar OS8 från en RK05 disk (2.5 MB):

http://www.youtube.com/watch?v=ByLp9A1nn7U.

Disken är öppen så läshuvudet syns...

Och datorspel är så klart inget nytt. PDP8, en VT52 terminal och "Adventure" :

http://www.youtube.com/watch?v=TJdq3gK6M78

Och en öppen RK05'a som kör en disk test (från en PDP8) :

http://www.youtube.com/watch?v=Laz-bG8eXYM

http://www.youtube.com/watch?v=5rt8kAcyU4Q

http://www.youtube.com/watch?v=qIXfkZX2XG4

- Anahka1975

- Inlägg: 1303

- Blev medlem: 30 augusti 2006, 21:49:46

- Ort: Säffle

Re: PDP8 Renovering

Ok. Tack för svaret. De sista länkarna "disk-test" såg mer ut att passa i senaste svarvningen tråden

Re: PDP8 Renovering

Det fanns även en pdp15 på Elektronmusikstudion i Stockholm där den styrde en av dåtidens mest avancerade synthar

http://sv.wikipedia.org/wiki/Elektronmusikstudion

Den här bilden är nog lite senare men det är samma kontrollyta, datorn stod i ett angränsande rum.

Det finns en rolig film om stället, kolla här:

http://sv.wikipedia.org/wiki/Elektronmusikstudion

Den här bilden är nog lite senare men det är samma kontrollyta, datorn stod i ett angränsande rum.

Det finns en rolig film om stället, kolla här:

- anders_bzn

- Inlägg: 5928

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Teletypen som jag har jag har visat tidigare i tråden har varit konsol till en tidig PDP-11, denna har styrt en sådan komponentmonteringsmaskin på Ericsson i Visby.sodjan skrev: På Ericsson hade i en PDP8e som styrde en sekvenseringsmaskin, d.v.s

en maskin som bandade om axiella komponenter (motstånd, dioder

och mindre kondingar) för att passa monteringsordningen

på kretskorten.

Alltså den maskin som fixar banden med komponenter som senare ska monteras

i en sådan här : http://www.youtube.com/watch?v=ktCJ6y-WN2U.

Notera att komponenterna kommer blandade på banhttp://www.youtube.com/watch?v=VEf2Xf7Urn8det, det var maskinen som

fixade det som hade en PDP8 hos oss...

PDP:n som renoveras i tråden kommer från Centralsjukhuset i Karlstad, där har den styrt en medicinsk analysmaskin. Jag har även en PDP-8/A som kommer därifrån. Den har stått på ett lab där den används till att mäta gångtiden i hörselnerven. Rulle: Hjälp mig med att fylla i detaljerna.

Sodjan: Jag fastnade på Youtube en lång stund och hittade denna:

Angående EMS, jag önskar att någon kunde dokumenterat det teknikhistoriska ännu mer. Jag skulle vilja se hela stället på tekniska museet (men det är ju försent).

Re: PDP8 Renovering

Det var en särdeles ovanlig symbol för d-vippan.anders_bzn skrev:Och det körde faktiskt som det skulle, men någon seriedata fick jag inte ut, bara någon dip i kurvan som kom med en frekvens på 11Hz (detta är bra, ty 110 baud är 11 tecken per sekund!).

Så jag stoppade i mitt andra M707 (så heter TX kortet) och testade med det. Resultatet blev att programmet fastnade i TSF, JMP -1 loopen för kortet tyckte aldrig att det sänt färdigt. Detta betyder att detta kortet också var trasigt fast på ett annat sätt än det första.

Dessa två korten är de mest komplexa i hela PDP:n, inga andra kort har så många kretsar. Skiftregistret är uppbyggt av åtta flip-floppar och totalt på kortet sitter det åtta 7474 med två flip-floppar i varje kapsel. Dessa är ökända för att gå sönder (bland oss som lagar PDP-8). Så det blir att hänga på logikanalysatorn...

Edit: Schemat på TX-kortet finns här: http://www.abc80.net/docs/pdp8/modules/ ... _rev_D.pdf

Edit: Stavning

För den som vill slippa googla rätt på vad symbolen verkar betyda så har jag efter titt på ett modernare datablad kommit fram till detta:

pin - tecken - funktion

1 / 13 = Vänster bulle = _reset (aktivt låg)

4 / 10 = Höger bulle = _set (aktivt låg)

3 / 11 = C = clock (latchning sker på uppgående flank)

2 / 12 = D = data

6 / 8 = 0 = _Q (inverterad utgång)

5 / 9 = 1 = Q (icke inverterad utgång)

Det verkar som om kortet helt enkelt känner av ifall stoppbit'en finns kvar i skiftregistret nånstans och då betraktar utgången som "busy". Det borde i sin tur innebära att pausen mellan varje tecken är ungefär lika lång som ett tecken, d.v.s. med 110BPS får du bara ungefär 5CPS. Du vill nog senare gärna köra med så hög baudrate som det går att skrämma upp PDP'n till om du inte vill ha den där speciella känslan av att allt går odrägligt långsamt.

Jag tror att du kan komma halvlångt med bara oscilloskop, mät på hur långt datat kommer i skiftregistret med början på E6 och vidare via E8, E11, E15 och E2. Man man väl för övrigt konstatera att i princip alla signaler ska visa någon form av digital vågform så om du känner för att mäta utan att behöva orka tänka så kan du nog köra programmet och mäta med oscilloskop minst 0,2 sekunder på varje pinne hela kortet runt och se om det verkar saknas signal eller framförallt om logiknivåerna ser trasiga ut.

Det har nog nämnts femtioelva gånger förr i tråden men man ska inte förakta tricket att låta kortet vara igång en stund och sen känna vilka kretsar som verkar bli extra varma, och börja misstänka dem

Re: PDP8 Renovering

Hmm, jag kanske är gammal, men i mina ögon ser det ut som en väldigt standard symbol för en D-vippa. Kan iofs vara att jag är van vid amriska ritningar med. Har aldrig riktigt gillat den standard som lärdes ut i skolan när jag gick där. Allt var fyrkanter, och så skulle man rita i fyrkanterna vilken funktion det var, osv...

Jag ser inte hur du kan få ihop att TX är busy ett helt tecken efter att den har skickat ut tecknet. Ett nytt värde att skickas ut laddas i vipporna genom alla NAND-grindar i toppen (E4, E5, E7). LINE laddas i detta läge från ACTIVE, och blir därmed startbit (eftersom ACTIVE blir aktiv när man ska börja skicka). Därefter skiftas tecknet upp ett steg i taget med hjälp av klockan, och att D-ingången för varje bit kommer från den normala utgången på D-vippan innan. Första D-vippan har ingången jordad, så allt eftersom tecknet skiftas ut så laddas alla D-vippor med 0. Enable laddas med 1 för att börja skicka, så det finns en 1 i slutet av det tecken som skall skickas ut. Om jag läser rätt så kommer ACTIVE sedan att vara inaktiv under tiden själva tecknet skickas. När själva datat skickats klart så drar ACTIVE igen medans stopp-bitten skickas.

Inverterade utgångarna från D-vipporna går till en NAND (E9). När så nästan alla D-vippor är 0 (bit 2-bit 8 för att vara exakt) i kombination med AH1, så kommer E9 att börja dra. Då är i princip transmit klar. I det läger sitter enable-bitten vid E2 (bit 1), och sista databitten sitter i också i E2 (LINE). I detta läge så är det bara stopp-bitten kvar som ska genereras. Och det hanteras genom ACTIVE-signalen som håller "rätt" längd. Det är lite tjorvigt med den biten, eftersom man kan välja att ha 1, 1.5 eller 2 stoppbittar.

Men ACTIVE signalen ser sedan till att hålla kvar stopp-bitten i rätt längd.

E16 (FLAG) sätts ju sedan när hela tecknet har skickats ut, men D-vippan klockas inte in förrän stop-bitten också skickats (går på ACTIVE-signalen). Och SKIP till CPU baserar sig sedan på FLAG.

Så när hela tecknet, inklusive start och stopp-bittar skickats, så indikeras att TX nu inte längre är aktiv, och ett nytt tecken kan genast påbörjas.

Ingen mer fördröjning än den som faktiskt behövs.

Jag ser inte hur du kan få ihop att TX är busy ett helt tecken efter att den har skickat ut tecknet. Ett nytt värde att skickas ut laddas i vipporna genom alla NAND-grindar i toppen (E4, E5, E7). LINE laddas i detta läge från ACTIVE, och blir därmed startbit (eftersom ACTIVE blir aktiv när man ska börja skicka). Därefter skiftas tecknet upp ett steg i taget med hjälp av klockan, och att D-ingången för varje bit kommer från den normala utgången på D-vippan innan. Första D-vippan har ingången jordad, så allt eftersom tecknet skiftas ut så laddas alla D-vippor med 0. Enable laddas med 1 för att börja skicka, så det finns en 1 i slutet av det tecken som skall skickas ut. Om jag läser rätt så kommer ACTIVE sedan att vara inaktiv under tiden själva tecknet skickas. När själva datat skickats klart så drar ACTIVE igen medans stopp-bitten skickas.

Inverterade utgångarna från D-vipporna går till en NAND (E9). När så nästan alla D-vippor är 0 (bit 2-bit 8 för att vara exakt) i kombination med AH1, så kommer E9 att börja dra. Då är i princip transmit klar. I det läger sitter enable-bitten vid E2 (bit 1), och sista databitten sitter i också i E2 (LINE). I detta läge så är det bara stopp-bitten kvar som ska genereras. Och det hanteras genom ACTIVE-signalen som håller "rätt" längd. Det är lite tjorvigt med den biten, eftersom man kan välja att ha 1, 1.5 eller 2 stoppbittar.

Men ACTIVE signalen ser sedan till att hålla kvar stopp-bitten i rätt längd.

E16 (FLAG) sätts ju sedan när hela tecknet har skickats ut, men D-vippan klockas inte in förrän stop-bitten också skickats (går på ACTIVE-signalen). Och SKIP till CPU baserar sig sedan på FLAG.

Så när hela tecknet, inklusive start och stopp-bittar skickats, så indikeras att TX nu inte längre är aktiv, och ett nytt tecken kan genast påbörjas.

Ingen mer fördröjning än den som faktiskt behövs.

- anders_bzn

- Inlägg: 5928

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Jag har förstås kollat på detta under tiden som ni klurat ut hur det fungerar. bqt har rätt i hur det borde fungera och det gör det också! Fast bara för första tecknet. Det som händer sen är intressant.

Under tiden som stoppbiten håller på att klockas ut går transmittflaggan ner och det är möjligt att klocka in nästa tecken. Då ska vippan "flag" slå om eftersom TX då är upptaget med nästa tecken. Detta händer inte eftersom "CLEAR FLAG 1" är ständigt låg. Denna drivs av IOP 2, alltså ett av IO tillstånden. Det är alltså förmodligen fel i CPU:n och inte i TX kortet.

Eftersom "flag" vippan inte inte slår om så kommer programmet snurra vidare och klocka in nästa tecken och nästa med följden att allt bara går i sig.

Har bara hunnit kolla lite på detta, men blir det en timma till i kväll i labbet så kanske det löser sig!

Under tiden som stoppbiten håller på att klockas ut går transmittflaggan ner och det är möjligt att klocka in nästa tecken. Då ska vippan "flag" slå om eftersom TX då är upptaget med nästa tecken. Detta händer inte eftersom "CLEAR FLAG 1" är ständigt låg. Denna drivs av IOP 2, alltså ett av IO tillstånden. Det är alltså förmodligen fel i CPU:n och inte i TX kortet.

Eftersom "flag" vippan inte inte slår om så kommer programmet snurra vidare och klocka in nästa tecken och nästa med följden att allt bara går i sig.

Har bara hunnit kolla lite på detta, men blir det en timma till i kväll i labbet så kanske det löser sig!

Re: PDP8 Renovering

Hmm. Jag hoppas du noterat kommentaren vid E4 pinne 12,13: ("Connect to Clear Flag 2 when using in some half duplex systems"). Jag hoppas också att bygling för 5 eller 8 bitar data, respektive någon bygling för stopp-bit finns på plats, för annars lär det inte fungera som det ska.

Om jag läser ritningen rätt så ska nog Clear Flag 2 alltid vara hög normalt. Clear Flag 1, i kombination med rätt device kod är nog den väg som FLAG normalt ska nollställas. RTredje sättet som FLAG kan nollställas på är I/O Clear, som nog är en generell reset-signal i systemet.

6042 eller 6046 borde normalt nollställa FLAG. Du kan ju labba med det. Kör en tight loop med bara 6042, och mät reset-pinnen på FLAG D-vippan (E16).

Om jag läser ritningen rätt så ska nog Clear Flag 2 alltid vara hög normalt. Clear Flag 1, i kombination med rätt device kod är nog den väg som FLAG normalt ska nollställas. RTredje sättet som FLAG kan nollställas på är I/O Clear, som nog är en generell reset-signal i systemet.

6042 eller 6046 borde normalt nollställa FLAG. Du kan ju labba med det. Kör en tight loop med bara 6042, och mät reset-pinnen på FLAG D-vippan (E16).

- anders_bzn

- Inlägg: 5928

- Blev medlem: 17 december 2008, 19:22:18

- Ort: Kävlinge

- Kontakt:

Re: PDP8 Renovering

Jag har gjort detta, jag delade upp 6046 (TLS) i opkoderna 6062/6064 (jag kan inte mnemonicen för dessa).

Sen konstaterade jag att IOP2 inte är tillståndet (man ska aldrig anta något). Tillståndet heter IOP B och IOP2 är i stort sett IOP B & MB10(I) & IO ENABLE. Det intessanta är att MB10(I) motsvarar clear biten i IOT instruktionen, detta gör att 6062 inte fungerar! Mäter man på MB10(I) så är dem alltid noll även när man man exekverar 6062, inte rätt!

Nu används inte MB10(I) på mer än fyra ställen i maskinen och troligtvis sitter den fast i jord någonstans. MB10(0) används på desto fler ställen... Troligtvis fungerar inte heller "AC double shift left" och "AC double shift right".

Jag har på några ställen hittat små tennkulor som fastnat i flussmedlet (nej, jag löder inte varmt 300grader C, men mitt tenn är inte nytt) och mellan pad/pad eller pad/bana på kortet. Detta är lite svårt att se även om man kollar noga. Detta har hänt på kanske två ställen hittills. Nu har jag beställt riktigt flussrengörningsmedel och en LED-belyst lupp. Fast jag kanske borde kanske gå till optikern och kolla om inte glasögonen borde uppgraderas.

Sen konstaterade jag att IOP2 inte är tillståndet (man ska aldrig anta något). Tillståndet heter IOP B och IOP2 är i stort sett IOP B & MB10(I) & IO ENABLE. Det intessanta är att MB10(I) motsvarar clear biten i IOT instruktionen, detta gör att 6062 inte fungerar! Mäter man på MB10(I) så är dem alltid noll även när man man exekverar 6062, inte rätt!

Nu används inte MB10(I) på mer än fyra ställen i maskinen och troligtvis sitter den fast i jord någonstans. MB10(0) används på desto fler ställen... Troligtvis fungerar inte heller "AC double shift left" och "AC double shift right".

Jag har på några ställen hittat små tennkulor som fastnat i flussmedlet (nej, jag löder inte varmt 300grader C, men mitt tenn är inte nytt) och mellan pad/pad eller pad/bana på kortet. Detta är lite svårt att se även om man kollar noga. Detta har hänt på kanske två ställen hittills. Nu har jag beställt riktigt flussrengörningsmedel och en LED-belyst lupp. Fast jag kanske borde kanske gå till optikern och kolla om inte glasögonen borde uppgraderas.