Avkopplingskondensatorer - Design regler

Avkopplingskondensatorer - Design regler

Vilka design regler gäller vid placering av avkopplingskondensatorer m a p digital o analog elektronik? Tänker framför allt på ledningsdragning vs vior på kretskort.

mer kondingar än vad du normalt tror, och även att ha några halvsmå med, 0.1µf parallellt med 100pf eller så vid snabba saker

på störkänsliga saker så räcker det inte med enbart kondingar utan man ska ha lite resistans eller induktans mellan mating och krets

exempelvis mikrofonförstärkare eller likvärdigt

kraftiga jordplan är inte dumt det heller

på hfkretsar så strör jag ut kondingar, hellre för många än för få

på störkänsliga saker så räcker det inte med enbart kondingar utan man ska ha lite resistans eller induktans mellan mating och krets

exempelvis mikrofonförstärkare eller likvärdigt

kraftiga jordplan är inte dumt det heller

på hfkretsar så strör jag ut kondingar, hellre för många än för få

- bengt-re

- EF Sponsor

- Inlägg: 4829

- Blev medlem: 4 april 2005, 16:18:59

- Skype: bengt-re

- Ort: Söder om söder

- Kontakt:

Som sgat jättesvår - avkoppla matning nära kretsarna är alltid en bra idé dock. Att dela av matningsplan med ferriter är inte heller det en tokig idé i de fall man KAN dela av kretsarna till separata "block" på samma kort. Att göra korten så små som möjligt är också bra - välj alltid minsta kapseln du kan löda...

i övrigt - och analaga kretsar - koppla av matning väl - är det både HF och LF så behöver du både keramer och E-lytar för att koppla av hela bandet.

i övrigt - och analaga kretsar - koppla av matning väl - är det både HF och LF så behöver du både keramer och E-lytar för att koppla av hela bandet.

och glöm inte den hela, icke sönderslitsade jordplanet under alltihop...

Jag vet att det är jättesvårt vid hobby-cadning och har bara 2 lager att arbeta med - men det är bättre att använda 0-Ohmsmotstånd på komponentsidan för att hoppa över ledare än att med via gå till jordplansidan och skära sönder jordplanet med ledare...

Jag vet att det är jättesvårt vid hobby-cadning och har bara 2 lager att arbeta med - men det är bättre att använda 0-Ohmsmotstånd på komponentsidan för att hoppa över ledare än att med via gå till jordplansidan och skära sönder jordplanet med ledare...

Bl.a. därför är virning en bra metod för hobbyister som bara skall göra ett exemplar. En 100nF över varje krets och matning i form av två "gafflar" SOM går ihopa från sidorna på kortet. Alla avkopplingarna gör detta till ett drägligt jordplan och virtrådar är bra mycket mindre benägna att orsaka problem än banor på ett kort. Dessutom är saken färdigbyggd och igång ofta snabbare än mönstret till ett kort hunnit bli klart.

Stora elektrolyter vid spänningsmatningen. Och mindre kondesatorer nära

kretsen Vcc. Samt att där en kondensator behövs ska det finnas minst en till

parallellt för att täcka olika flanktider samt förhindra resonans.

Xilinx har bra applikations dokument på detta.

Kondensator - Induktans - Kondensator (CLC) filter kan med fördel användas för

att avskilja störningar mellan matningar.

kretsen Vcc. Samt att där en kondensator behövs ska det finnas minst en till

parallellt för att täcka olika flanktider samt förhindra resonans.

Xilinx har bra applikations dokument på detta.

Kondensator - Induktans - Kondensator (CLC) filter kan med fördel användas för

att avskilja störningar mellan matningar.

- Illuwatar

- Inlägg: 2256

- Blev medlem: 10 november 2003, 14:44:27

- Skype: illuwatar70

- Ort: Haninge

- Kontakt:

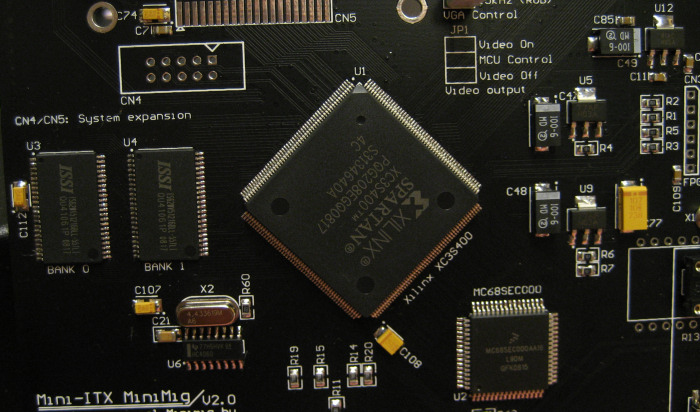

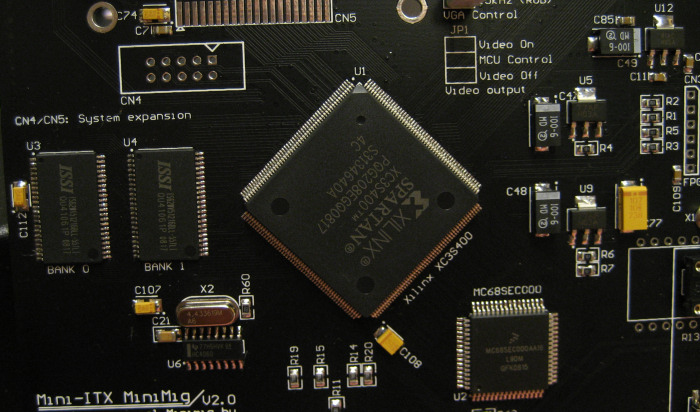

Jag kan ge ett exempel på avkoppling av en komponent med multipla matningsspänningar (en FPGA):

Här syns tydligt de olika tantalkondensatorerna av olika storlekar som hjälper till att hålla spänningarna uppe vid större strömuttag. Till höger syns de tre LDO-regulatorerna som förser FPGAn och dess kringkretsar med 3.3V, 2.5V och 1.25V. Alla dessa har egen avkoppling. Dessutom finns en buffertkondensator vid inkommande 5V (gula till höger).

Då har vi undersidan. Där ses alla 10nF keramiska (här storlek 0805) som avkopplar alla matningsspänningsben hos FPGAn. En 10nF per ben och så nära som möjligt. Utöver dessa finns några 100nF mellan alla dessa 10nF. Solida jordplan finns på båda sidor av kortet (som är 2-lagers i detta fall).

Detta på en design som inte arbetar med så extrema frekvenser. Infrekvensen till FPGAn ligger på knappa 5 MHz och snabbaste signalerna ut är ca 7 MHz. Kör man sina grejer högre upp är det multilayerkort som gäller och ännu mer noggrann avkoppling och avstörning som gäller.

Här syns tydligt de olika tantalkondensatorerna av olika storlekar som hjälper till att hålla spänningarna uppe vid större strömuttag. Till höger syns de tre LDO-regulatorerna som förser FPGAn och dess kringkretsar med 3.3V, 2.5V och 1.25V. Alla dessa har egen avkoppling. Dessutom finns en buffertkondensator vid inkommande 5V (gula till höger).

Då har vi undersidan. Där ses alla 10nF keramiska (här storlek 0805) som avkopplar alla matningsspänningsben hos FPGAn. En 10nF per ben och så nära som möjligt. Utöver dessa finns några 100nF mellan alla dessa 10nF. Solida jordplan finns på båda sidor av kortet (som är 2-lagers i detta fall).

Detta på en design som inte arbetar med så extrema frekvenser. Infrekvensen till FPGAn ligger på knappa 5 MHz och snabbaste signalerna ut är ca 7 MHz. Kör man sina grejer högre upp är det multilayerkort som gäller och ännu mer noggrann avkoppling och avstörning som gäller.

Kanske något för fler att läsa och förstå.

Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitor

http://www.xilinx.com/bvdocs/appnotes/xapp623.pdf

Power Distribution System (PDS) Design: Using Bypass/Decoupling Capacitor

http://www.xilinx.com/bvdocs/appnotes/xapp623.pdf