Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Efter att en tjeckisk hemmagjord The Final Cartridge III kommit på tal på Lemon64.com, gjordes designen om av undertecknad för att passa i tillgängliga skal. Frågan uppstod sedan om man kunde göra en Action Replay 6 till vår Commodore 64...

AR6 har i original ett RAM på 8kB, ROM på 32kB, special-logik krets (ASIC gissar jag) samt freeze- och reset-knapp.

Det finns kloner av denna med några lokigkretsar och en bipolär PROM som programmerats med en tabell för att styra typ av cartridge samt enable för rom och ram beroende på data- och adress-signaler.

Här är ett schema för en sådan klon:

http://zimmers.net/anonftp/pub/cbm/sche ... zer/MK.gif Efter att ha ritat upp en design efter detta schema och sedan insett att ett bipolärt PROM kanske borde undvikas i brist på programmerare och tillgänglighet (även om det inte är svårt att hitta på eBay) så bestämde jag att man kanske skulle testa att göra en fil för en Xilinx XC9536 CPLD som använts för t.ex. PLA ersättare i C64.

Jag har kommit så långt att jag har lagt in tabellen som skulle programmerats i PROM:et, ligger som en modul i schemat där den främsta "programmeringen" gjorts genom att försöka återskapa schemat i bilden ovan. Har sedan fått igenom hela designen genom syntetisering utan fel och med bara en varning "Unable to retrieve the path to the iSE Project Repository. Will use the default filename of 'AR6_schematic.ise'." Detta är dock en varning man kan strunta i enligt Xilinx supportsida.

Det var 20 år sen jag gjorde något i VHDL så det är nästan som att börja om från början. Tänkte om någon var sugen på att kika lite så man kanske kan få hjälp att undvika nybörjarfel.

Någon som vill kika, vilka filer är intressanta? Det är ju en hel drös med filer, ser inte någon "städa" funktion någonstans.

Jag har lagt ut signalerna så vettigt jag kan, det är väl dags att CAD:a ett experimentkort (med JTAG) och testa...

Här är schemat jag pusslat ihop i ISE Project Navigator: Något som ser konstigt ut, några bra tips?

AR6 har i original ett RAM på 8kB, ROM på 32kB, special-logik krets (ASIC gissar jag) samt freeze- och reset-knapp.

Det finns kloner av denna med några lokigkretsar och en bipolär PROM som programmerats med en tabell för att styra typ av cartridge samt enable för rom och ram beroende på data- och adress-signaler.

Här är ett schema för en sådan klon:

http://zimmers.net/anonftp/pub/cbm/sche ... zer/MK.gif Efter att ha ritat upp en design efter detta schema och sedan insett att ett bipolärt PROM kanske borde undvikas i brist på programmerare och tillgänglighet (även om det inte är svårt att hitta på eBay) så bestämde jag att man kanske skulle testa att göra en fil för en Xilinx XC9536 CPLD som använts för t.ex. PLA ersättare i C64.

Jag har kommit så långt att jag har lagt in tabellen som skulle programmerats i PROM:et, ligger som en modul i schemat där den främsta "programmeringen" gjorts genom att försöka återskapa schemat i bilden ovan. Har sedan fått igenom hela designen genom syntetisering utan fel och med bara en varning "Unable to retrieve the path to the iSE Project Repository. Will use the default filename of 'AR6_schematic.ise'." Detta är dock en varning man kan strunta i enligt Xilinx supportsida.

Det var 20 år sen jag gjorde något i VHDL så det är nästan som att börja om från början. Tänkte om någon var sugen på att kika lite så man kanske kan få hjälp att undvika nybörjarfel.

Någon som vill kika, vilka filer är intressanta? Det är ju en hel drös med filer, ser inte någon "städa" funktion någonstans.

Jag har lagt ut signalerna så vettigt jag kan, det är väl dags att CAD:a ett experimentkort (med JTAG) och testa...

Här är schemat jag pusslat ihop i ISE Project Navigator: Något som ser konstigt ut, några bra tips?

Du har inte behörighet att öppna de filer som bifogats till detta inlägg.

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Ett sidospår:

Det länkade orginal-"pirat"-schemat verkar ju inte helt jättebra om jag tolkar det rätt.

När _RESET dras låg, antingen av knappen eller än värre från datorns egen resetkrets, så dras _CL låg på U6B varpå dess _Q går hög men utspänningen kortsluts via en 1N4148 tillbaka till _RESET som dragits låg. Förvisso är det kort tid detta sker, TTL tål väl kortslutning mot jord inom vissa gränser och datorns drivkretsar för _RESET ska väl vara acceptabelt starka (för att orka allt, de äldsta C64 och framförallt alla VIC-20 hade dessutom "IEC"-seriebussens resetpinne ansluten direkt till datorns resetledning). Det är väl ändå ingen vidare design...

Ett annat sidospår:

Hur går det med dina cartridges för Fairchild Channel F?

Det är kanske klart krångligare men något som vore trevligt att ha i programmerbar logik vore väl en kopia på Fairchild 3853 SMI?

Det länkade orginal-"pirat"-schemat verkar ju inte helt jättebra om jag tolkar det rätt.

När _RESET dras låg, antingen av knappen eller än värre från datorns egen resetkrets, så dras _CL låg på U6B varpå dess _Q går hög men utspänningen kortsluts via en 1N4148 tillbaka till _RESET som dragits låg. Förvisso är det kort tid detta sker, TTL tål väl kortslutning mot jord inom vissa gränser och datorns drivkretsar för _RESET ska väl vara acceptabelt starka (för att orka allt, de äldsta C64 och framförallt alla VIC-20 hade dessutom "IEC"-seriebussens resetpinne ansluten direkt till datorns resetledning). Det är väl ändå ingen vidare design...

Ett annat sidospår:

Hur går det med dina cartridges för Fairchild Channel F?

Det är kanske klart krångligare men något som vore trevligt att ha i programmerbar logik vore väl en kopia på Fairchild 3853 SMI?

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Det hade ju absolut varit trevligt med en SMI i VHDL, ska tydligen finnas redan men det är inte alla som vill dela med sig av saker som de ägnat en massa tid att göra.

Man kanske hade kunnat göra något dugligt redan nu trots den bristfälliga och ibland felaktiga dokumentationen. Men jag tror jag avvaktar tills jag inte kan få tag på originalkretsar, så kanske någon annan hunnit före.

Man kanske hade kunnat göra något dugligt redan nu trots den bristfälliga och ibland felaktiga dokumentationen. Men jag tror jag avvaktar tills jag inte kan få tag på originalkretsar, så kanske någon annan hunnit före.

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Dokumentationen verkar ju "sådär"...

Jag läste en del i F8 User's Guide (1976)(Fairchild)(Document 67095665)-1 och på omkring pdf-sid 90 till 103 så verkar det vara rätt hyggligt förklarat hur ROMC-signalerna fungerar och hur anslutna enheter (3851,3852,3853,3861) ska agera på CPU'ns styrning av ROMC-signalerna.

Om man vill implemetera en egen SMI så lär man väl i stort sett "bara" behöva implementera registrerna (PC0, PC1, DC0, DC1), logiken för att inkrementera dem och för att skyffla data mellan dem, extern adressbuss, extern databuss och "intern" databuss. De ROMC-grejer som kräver att två saker görs av en SMI kan väl implementeras genom att sakerna utförs på olika klockflanker. Man lär nog få ha en (ring)räknare som stegas av klockpulsen och nollställs av "write" för att styra timingen rätt. Det blir väl inte busenkelt men en ungefärlig gissning är att man kan nog få plats med hela kalaset byggt med 74/40-logik i en cartridge, fast det lär bli på håret med utrymmet. Givetvis är programmerbar logik antagligen vettigare här, fast det är väl en frågan om man vill göra det "äkta vintage" eller inte.

Eventuella felaktigheter i dokumentationen borde väl gå att finna genom att köra en tillräckligt bra logikanalysator på de faktiska signalerna på en PSU, DMI eller SMI?

Men en märklig grej jag noterar är att det finns instruktioner för att växla DC0 och DC1, vissa enheter (DMI om jag minns rätt) har bara DC0, och ROMC-funktionerna för läsning relaterade till DC0 är specade så att den enhet vars minne utpekas av DC0 ska driva bussen. Det gör att om man har ett system med en DMI och en PSU eller SMI, d.v.s. ett system som både har enheter med och utan DC1, så borde det kunna med mjukvara gå att orsaka motdrivning av databussen. Jag tänker att man ser till att ladda DC1 med en adress i PSU/SMI och DC0 med en adress i DMI, växlar DC1 med DC0 och sen läser relaterat till DC0. Då kommer PSU/SMI'ns DC0 peka på en adress i PSU/SMI medan DC0 i DMI kommer peka på en adress i DMI, och om de inte råkar innehålla exakt samma data så blir det motdrivning. Bussen kanske tål det, men det visar väl på en brist i konstruktionen.

Lite lustigt är att de håller sig inte ens till sina egna benämningar inom dokumentet. Schemat på PDF-sida 323 pratar om ROM istället för PSU och MI istället för SMI...

Jag läste en del i F8 User's Guide (1976)(Fairchild)(Document 67095665)-1 och på omkring pdf-sid 90 till 103 så verkar det vara rätt hyggligt förklarat hur ROMC-signalerna fungerar och hur anslutna enheter (3851,3852,3853,3861) ska agera på CPU'ns styrning av ROMC-signalerna.

Om man vill implemetera en egen SMI så lär man väl i stort sett "bara" behöva implementera registrerna (PC0, PC1, DC0, DC1), logiken för att inkrementera dem och för att skyffla data mellan dem, extern adressbuss, extern databuss och "intern" databuss. De ROMC-grejer som kräver att två saker görs av en SMI kan väl implementeras genom att sakerna utförs på olika klockflanker. Man lär nog få ha en (ring)räknare som stegas av klockpulsen och nollställs av "write" för att styra timingen rätt. Det blir väl inte busenkelt men en ungefärlig gissning är att man kan nog få plats med hela kalaset byggt med 74/40-logik i en cartridge, fast det lär bli på håret med utrymmet. Givetvis är programmerbar logik antagligen vettigare här, fast det är väl en frågan om man vill göra det "äkta vintage" eller inte.

Eventuella felaktigheter i dokumentationen borde väl gå att finna genom att köra en tillräckligt bra logikanalysator på de faktiska signalerna på en PSU, DMI eller SMI?

Men en märklig grej jag noterar är att det finns instruktioner för att växla DC0 och DC1, vissa enheter (DMI om jag minns rätt) har bara DC0, och ROMC-funktionerna för läsning relaterade till DC0 är specade så att den enhet vars minne utpekas av DC0 ska driva bussen. Det gör att om man har ett system med en DMI och en PSU eller SMI, d.v.s. ett system som både har enheter med och utan DC1, så borde det kunna med mjukvara gå att orsaka motdrivning av databussen. Jag tänker att man ser till att ladda DC1 med en adress i PSU/SMI och DC0 med en adress i DMI, växlar DC1 med DC0 och sen läser relaterat till DC0. Då kommer PSU/SMI'ns DC0 peka på en adress i PSU/SMI medan DC0 i DMI kommer peka på en adress i DMI, och om de inte råkar innehålla exakt samma data så blir det motdrivning. Bussen kanske tål det, men det visar väl på en brist i konstruktionen.

Lite lustigt är att de håller sig inte ens till sina egna benämningar inom dokumentet. Schemat på PDF-sida 323 pratar om ROM istället för PSU och MI istället för SMI...

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Jag har försökt få till en dumpare så jag kan dumpa spelkassetterna - även om man följer databladen exakt så lyckas det inte för alla kassetter - även om spelet fungerar i konsollen. Så saker och ting stämmer inte men det är sant att man med hjälp av ROMC signalerna skulle kunna lösa det mesta, i spelet jobbar man mot en CPU och två PSU:er (3850 + 2 x 3851) som sitter i konsollen.

Det är väl den där timern i 3853 som ställer till det också, inte för att jag vet säkert om det är någon känd programkod som nyttjar den, det skulle kunna vara i Schack-spelet eller senare spel som misstänks bestå av ett SMI-chip och "normal" rom istället för PSU:er (3851).

Det är väl den där timern i 3853 som ställer till det också, inte för att jag vet säkert om det är någon känd programkod som nyttjar den, det skulle kunna vara i Schack-spelet eller senare spel som misstänks bestå av ett SMI-chip och "normal" rom istället för PSU:er (3851).

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Det är väl inte helt otänkbart att spelen består av proprietära special-PSU'er som kanske skiljer sig på något märkligt sätt? Förvisso inte så sannolikt men inte omöjligt med tanke på att Fairchild tillverkade både kretsarna och spelet.

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Det kanske ändrade sig under tiden, kanske finns andra puls-kombinationer som fungerar på allt men det är lite segt att experimentera sig fram till rätt sort.

Kanske man investerar i en enkel logik analysator och kikar ordentligt på konsollen någon dag.

Kanske man investerar i en enkel logik analysator och kikar ordentligt på konsollen någon dag.

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Jag har logikanalysator som stått i flera år, som jag mest bara provkört men inte riktigt orkat sätta mig in i hur den verkligen används.

Sidospår: Från början var den stående för att jag inte hade rätt kablar (den ansluts med "enpoliga stiftlist-honor", alltså den typ av sladdmonterade honor som är enpoliga och går att ansluta i valfri mängd invid varandra på en vanlig 2,54mm-delning-stiftlist). När jag väl skaffat kablarna så avstannade det hela på grund av att jag råkade hotwappa grafikkortet i datorn jag kör mot loginanalysatorn. Mjukvaran är för Windows 3.11 så jag rev fram en gammal P90, och skulle byta kort för det som satt i hittade jag inga vettiga win3.x-drivers för för att få vettig upplösning. Termostatreglerad fläkt i nätagget och så långsam CPU att det inte behövs CPU-fläkt (eller ens CPU-fläns vad jag minns) gjorde att jag trodde inte att datorn var på... Den mådde inte riktigt bra av det där, den "fungerar" men det blir rätt allvarliga grafikbuggar...

Jag borde gräva fram någon annan gammal Pentium-1-dator (eller nån 486:a) att köra Windows 3.11 på, och ta tag i analysatorn igen.

Fast först borde jag gräva fram mitt Fairchild Channel F. Jag har en liten aning om var det är, men är inte helt säker

Sidospår: Från början var den stående för att jag inte hade rätt kablar (den ansluts med "enpoliga stiftlist-honor", alltså den typ av sladdmonterade honor som är enpoliga och går att ansluta i valfri mängd invid varandra på en vanlig 2,54mm-delning-stiftlist). När jag väl skaffat kablarna så avstannade det hela på grund av att jag råkade hotwappa grafikkortet i datorn jag kör mot loginanalysatorn. Mjukvaran är för Windows 3.11 så jag rev fram en gammal P90, och skulle byta kort för det som satt i hittade jag inga vettiga win3.x-drivers för för att få vettig upplösning. Termostatreglerad fläkt i nätagget och så långsam CPU att det inte behövs CPU-fläkt (eller ens CPU-fläns vad jag minns) gjorde att jag trodde inte att datorn var på... Den mådde inte riktigt bra av det där, den "fungerar" men det blir rätt allvarliga grafikbuggar...

Jag borde gräva fram någon annan gammal Pentium-1-dator (eller nån 486:a) att köra Windows 3.11 på, och ta tag i analysatorn igen.

Fast först borde jag gräva fram mitt Fairchild Channel F. Jag har en liten aning om var det är, men är inte helt säker

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Har för mig att det tipsats om någon billig kinesisk kopia på något man petar in i usb-porten.

Hade ju varit spännande att kolla exakt vad som händer på riktigt, lägga några prober på cartridgen, skriva ett testprogram och sen läsa av.

Dumper-programmet finns här:

http://channelf.se/veswiki/index.php?ti ... art_dumper

Hade ju varit spännande att kolla exakt vad som händer på riktigt, lägga några prober på cartridgen, skriva ett testprogram och sen läsa av.

Dumper-programmet finns här:

http://channelf.se/veswiki/index.php?ti ... art_dumper

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Har lödat ihop en prototyp och testat min kod, funkade bara lite.

Jag får upp menyn på den tyska Action Cartridge Plus v6.0, men switchar jag rommet till vanliga AR6.0 så blir det lite skräp med ett streck under bara.

Av menyalternativen funkar reset och den går in i en andra meny om man trycker på restore. Det är väl bild och utskrifts-funktionen som ger någon slags funktion.

Kommer inte längre än så här med VHDL-schemat, har funderat på huruvida man behöver ordna med pull up funktion där det finns i detta diod-kluster... Kan såklart vara så att det blir bekymmer med timing. Får väl ge mig in i annan kod och se hur de gjort, EasyFlash, EasyFlash 3 t.ex.

Jag får upp menyn på den tyska Action Cartridge Plus v6.0, men switchar jag rommet till vanliga AR6.0 så blir det lite skräp med ett streck under bara.

Av menyalternativen funkar reset och den går in i en andra meny om man trycker på restore. Det är väl bild och utskrifts-funktionen som ger någon slags funktion.

Kommer inte längre än så här med VHDL-schemat, har funderat på huruvida man behöver ordna med pull up funktion där det finns i detta diod-kluster... Kan såklart vara så att det blir bekymmer med timing. Får väl ge mig in i annan kod och se hur de gjort, EasyFlash, EasyFlash 3 t.ex.

Du har inte behörighet att öppna de filer som bifogats till detta inlägg.

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

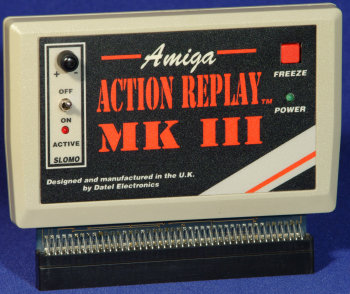

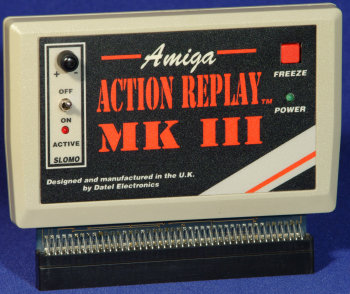

Troligen helt ovesäntligt i denna tråden.. men en sån här hade jag till min Amiga 500 i alla fall, fixade en till lillebrorsan åxå... tidigt 90 tal var det..

Re: Bygga Action Replay 6 med Xilinx CPLD, VHDL någon?

Sån där har jag också, men den kom lite senare.

Ingen som har erfarenhet av att göra om "riktig logik" till programmerbar?

Satt och tittade på VHDL-koden för Action/Retro Replay i EasyFlash/3 igår, det blir lite annorlunda när A.R. bara är en byggsten i en cartridge som gör flera olika saker - för det såg väldigt enkelt ut jämfört med den kod jag har fått fram.

Ingen som har erfarenhet av att göra om "riktig logik" till programmerbar?

Satt och tittade på VHDL-koden för Action/Retro Replay i EasyFlash/3 igår, det blir lite annorlunda när A.R. bara är en byggsten i en cartridge som gör flera olika saker - för det såg väldigt enkelt ut jämfört med den kod jag har fått fram.