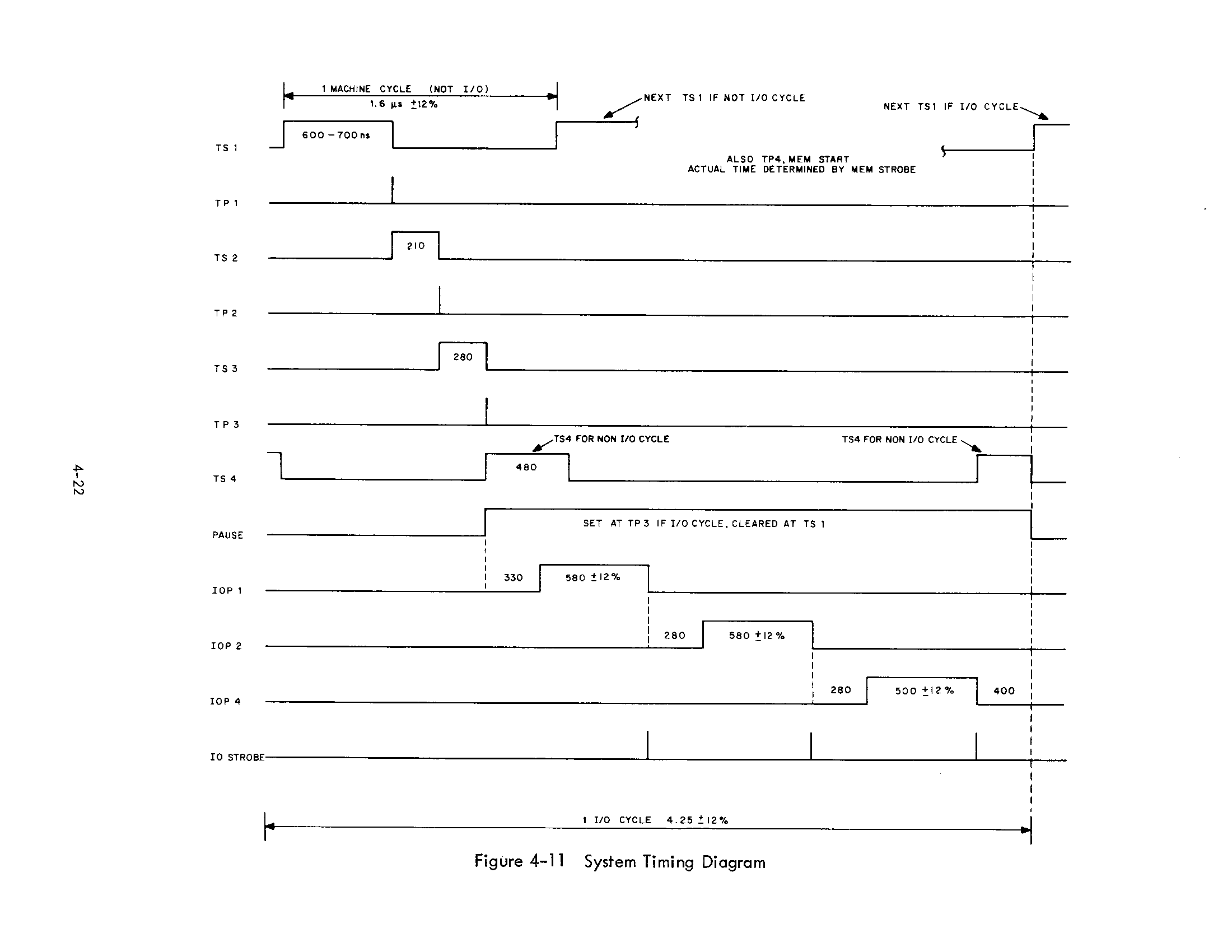

Jag bestämde mig för att mäta timing tillstånden. Det går fyra tillstånd på en komplett maskincykel, dessa heter TS1-TS4. I DECs manualer hittar man förstås facit på hur det ska se ut:

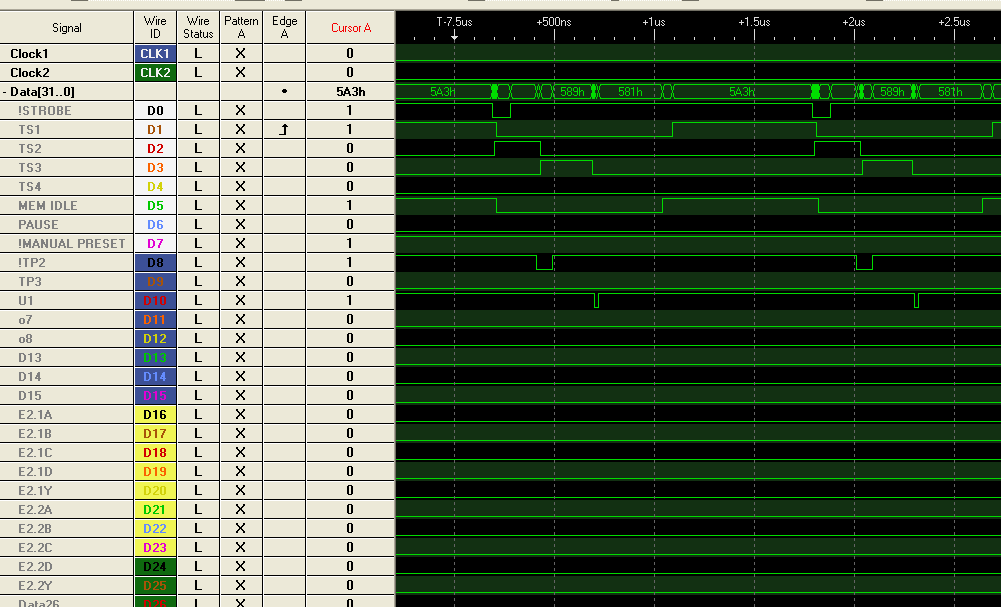

Sen är det ju bara att koppla in logikanalysatorn och kolla på hur det ser ut:

Man ser då (signalerna är inte i samma ordning) att TS4 saknas och det gör även TP3. TP3 är en tidspuls. Detta förklarar nog ett och annat. IOP signalerna saknas också men jag kör ingen IO instruktion så detta väntar jag lite med.

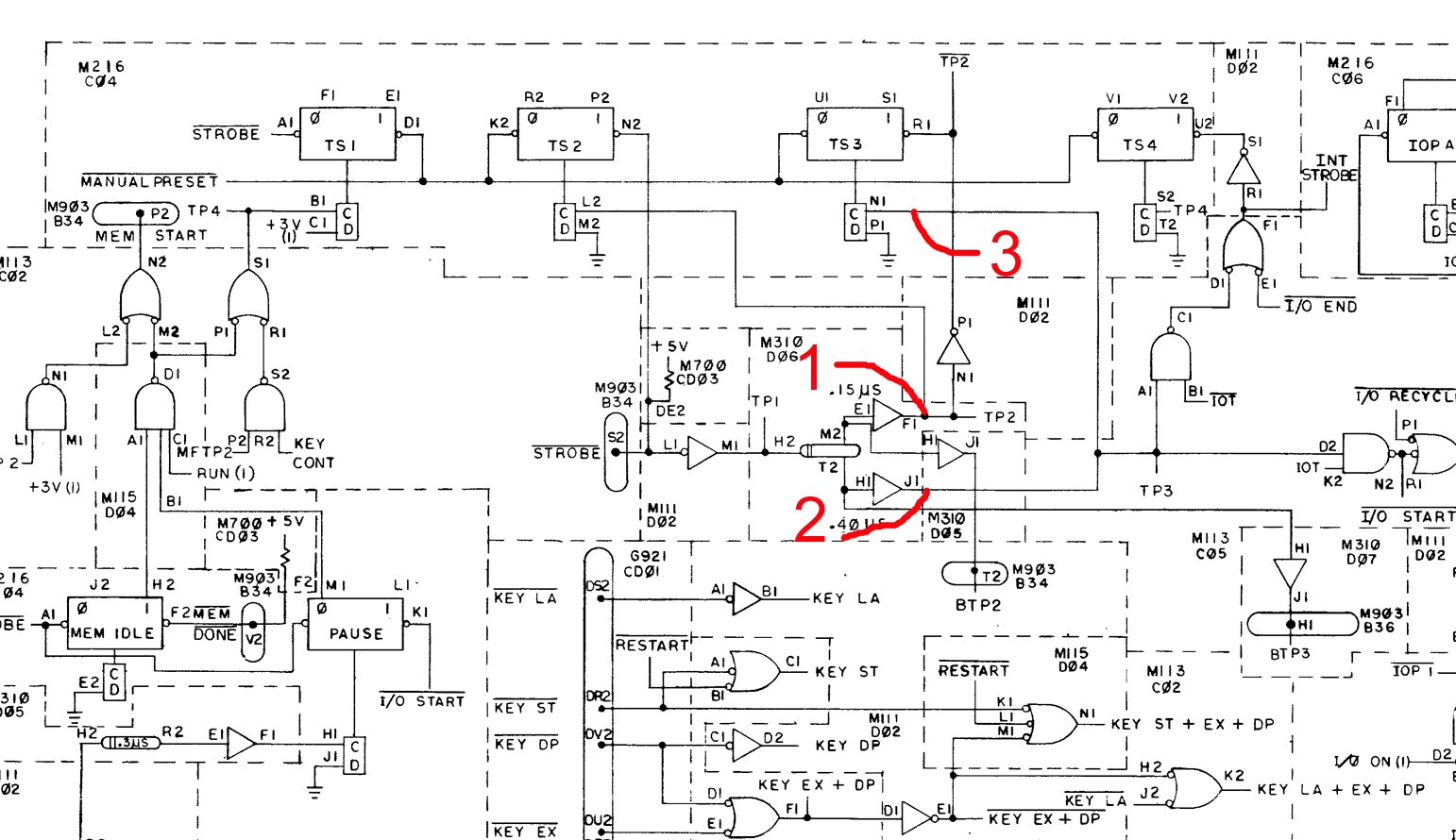

Man ser på schemat att TS3 inte heller borde fungera om TP3, vilken den inte heller gör hela tiden. Signalerna vid 1 och 2 är TP2 respektive TP3, båda kommer ifrån samma delay-line. TP2 fungerar men inte TP3. Jag mätte TP3 med oscilloskopet och konstaterade att pulserna visst finns men att amplituden på pulserna är knappt 1V. De borde vara över 3V...

Jag mätte även precis innan sista buffertkretsen vid (2) och där är amplituden som den ska. Alltså något lastar förmodligen ner signalen. Vippan, en 7474 som håller TS3 (och TS4) vid (3) byttes snabbt ut men det gjorde ingen skillnad. Bytte hela kortet med 2-ingångars NAND grindar som man ser till höger på schemat utan resultat. Förmodligen finns TP3 att hitta på något mer schemablad men det har jag inte hunnit kolla ännu.

Fortsättning följer...